Page 1

Loading page image...

Page 2

Loading page image...

Page 3

Loading page image...

Page 4

Loading page image...

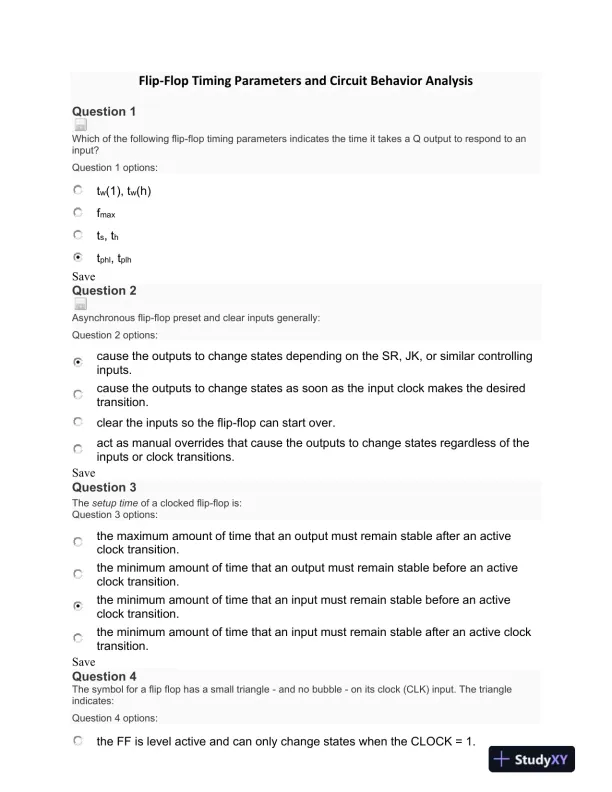

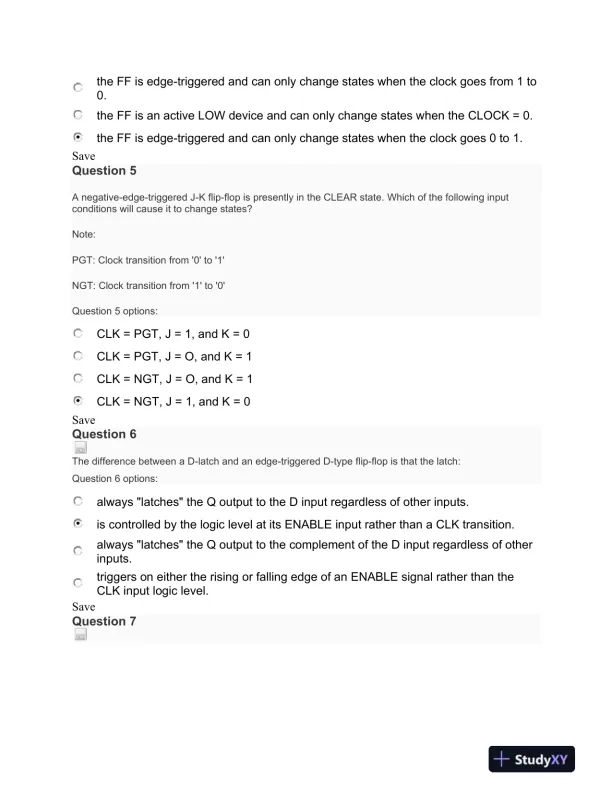

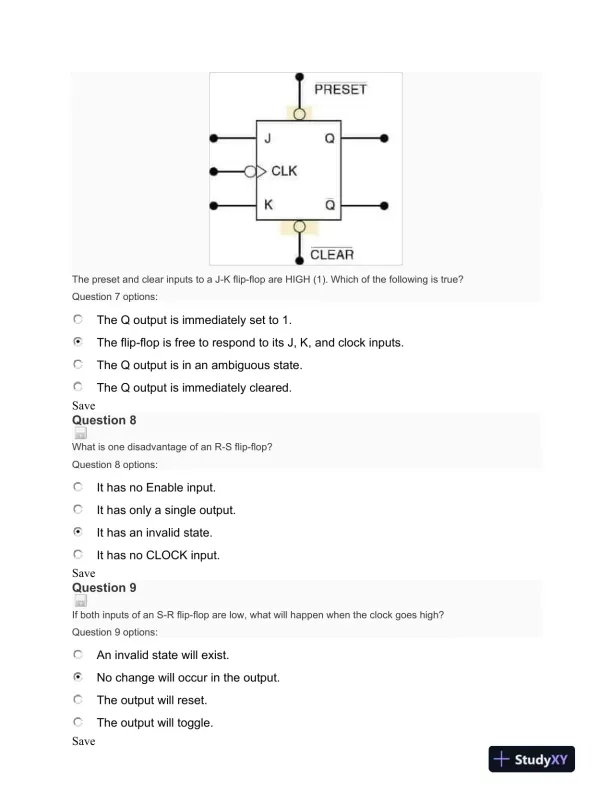

A study of flip-flop circuits and their timing characteristics.

Loading page image...

Loading page image...

Loading page image...

Loading page image...

This document has 11 pages. Sign in to access the full document!